이번 장에서는 FET의 게이트 단자가 기술의 발전에 따라, 혹은 당면한 문제를 해결해가는 과정에서 어떻게 발전하였는지에 대해 알아보도록 하겠습니다.

3개 단자(소스, 게이트, 드레인)를 만드는 방식

▲ 게이트/소스/드레인 단자들의 제조 방식(형태적/화학적 변화 기준) @ 수직단면구조

반도체 공정 방식은 크게 2가지로 나뉩니다. Substrate 계면인 기준선 위로는 주로 물리적 변화를 주고, 기준선 아래로는 물리적 변화를 일으킬 수 없기 때문에 주로 화학적 변화를 줍니다. FET의 3가지 단자 중, Substrate 계면 위쪽에 위치하는 게이트 단자는 증착을 시켜서 만들고, Substrate 계면 아래쪽에 위치하는 소스와 드레인 단자는 임플란팅과 확산을 시켜서 만듭니다. Sub 계면 이하의 영역에서 굳이 증착방식을 적용하려면 Trench 형식으로 Substrate를 필요한 부피만큼 파내고, 그 파낸 구덩이 속에 무언가를 채워 넣어야 하는데, 이렇게 하면 공정 Step과 비용이 증가합니다. Trench 방식을 적용하여 트랜지스터를 만들던 독일(유럽연방)의 최대 메모리 반도체 회사인 인피니언은 결국 공정원가의 증가로 인해 경쟁력을 상실하여 메모리 반도체 사업을 접었답니다.

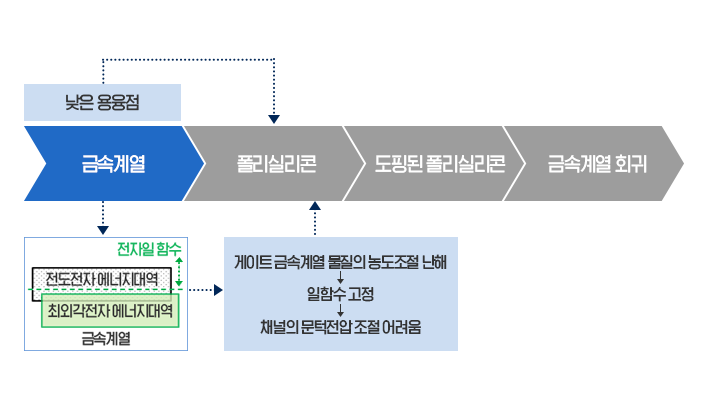

게이트 물질이 금속일 때 발생하는 문제

▲ 게이트 물질의 변천 : 금속계열 성분의 문제점

게이트 층은 전압을 전달해야 하기 때문에 전도성이 좋아야 하고, 되도록이면 저항성분이 없어야 이상적입니다. 그래서 초창기에는 저항 성분이 매우 낮은 금속 성분(ex. 알루미늄)으로 만들기도 했죠. 그러나 어떤 금속 성분은 반도체 공정에서 사용되는 높은 온도에 비해 용융온도가 낮기 때문에, 원하는 게이트 형태가 쉽게 무너질 수 있는 문제가 발생되었습니다. 또한 여기서 집고 넘어가야 하는 것은 게이트를 금속 성분으로 했을 경우, TR의 문턱전압의 조정이 폴리실리콘 물질보다는 어렵다는 문제입니다. 여러 가지 변수가 문턱전압에 영향을 끼치지만, 그 중에 게이트 물질에서 전자를 탈출 시키는 에너지(일함수)와 Substrate물질에서 전자를 탈출 시키는 에너지(일함수)의 차이도 문턱전압의 변수가 됩니다. 결국 금속물질의 문제는 최외각 전자를 탈출시키는 에너지를 쉽게 제어할 수 없어서 게이트를 사용할 경우 문턱전압을 조정하는 데 어려움을 겪는다는 것입니다. 따라서 게이트의 금속물질을 실리콘 계열로 변경할 필요성이 대두되었죠.

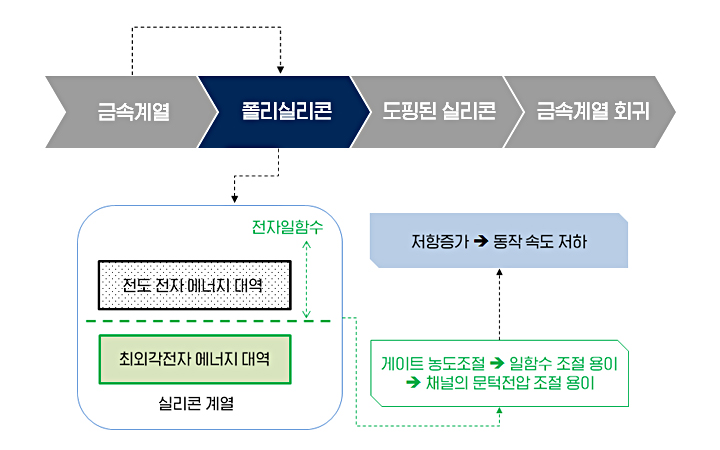

게이트 물질의 변천: 금속계열→폴리실리콘

▲ 게이트 물질의 변천 : 금속계열에서 폴리실리콘으로 변경

문턱전압을 낮추려면 게이트 물질의 원자를 구성하는 최외각전자가 탈출해야 하는 에너지를 조절할 수 있어야 합니다. 그래서 통제가 어려운 금속 대신 통제가 비교적 용이한 폴리 실리콘이라는 물질을 사용하게 된 것이죠. 또 게이트 단자의 기준물질로 실리콘을 쓸 경우 실리콘의 녹는 온도는 약 1,500도 섭씨 정도이므로, 금속의 용융점 보다는 월등히 높기 때문에 다른 확산공정 시 게이트의 형태적 변경은 거의 일어나지 않습니다. (실리콘이 녹을 정도면, 웨이퍼 전체가 녹아내리겠죠.) 폴리(다결정)실리콘은 전자가 원심력을 이겨내고 탈출하려는 에너지를 원하는 양으로 비교적 용이하게 조절할 수 있게 되었죠. 실질적으로는 게이트 단자를 형성하는 물질의 농도를 높였다가 내렸다가 하면 될 테니까요. 반도체는 화학성분의 농도를 적절히 사용하는 것이 매우 중요합니다. 더군다나 게이트의 기준물질로 실리콘을 사용하면, Substrate의 기본물질인 실리콘과 성격이 비슷해지기 때문에 에너지 밴드 내 에너지 갭(Energy Gap) 조절, 일함수 조절 등이 쉬워집니다. 그에 따라 채널의 문턱전압의 조절이 더욱 용이해지는 것이죠. 그런데 문제는 폴리실리콘이 금속에 비해 저항값이 몇 백배나 높다는 것입니다. 게이트 단자로 인가되는 전압은 게이트 단자 밑에 있는 게이트 옥사이드를 지나 Substrate 내 채널로 전계가 전달되어야 하는데요. 게이트의 저항이 높으면 게이트의 전압 전달 속도가 늦어지게 됩니다.

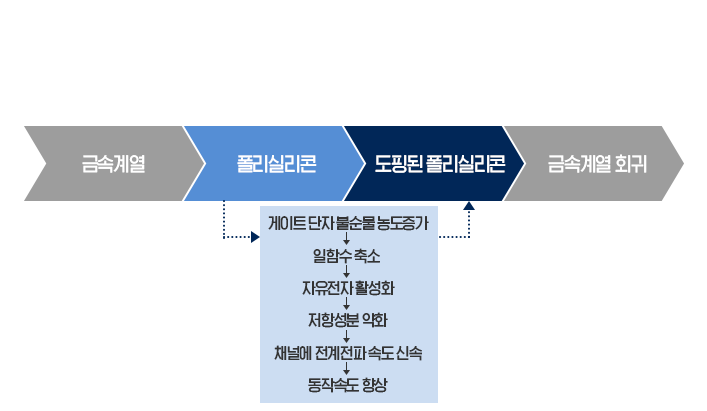

게이트 물질의 저항성을 낮춰라

▲ 게이트 물질의 변천 : 폴리실리콘에서 전도성성분 증가

따라서 저항 성분을 낮추려면 반대로 게이트에 전도성 성분을 더 추가해야 합니다. 따라서 게이트에 N_type/P_type 고농도를 추가로 도핑(임플란팅)하여 전기전도성을 높이기도 하고, 게이트 단자 위에 금속을 덧칠하기도 합니다. 불순물(13족/15족)을 폴리실리콘 위에 임플란팅(아류공정) 한 후에 온도를 실리콘 용융온도(약1,500도 섭씨)의 절반 정도로 가열해 게이트 상층에 임플란팅된 입자들을 게이트 영역 아래쪽으로 확산시킵니다. (여기서 게이트의 확산공정을 진행할 경우에는, 소스와 드레인 단자에 임플란팅을 한 후 3개 단자를 모두 같이 확산진행하면 시간과 열에너지 소모가 절약되지 않을까요?)

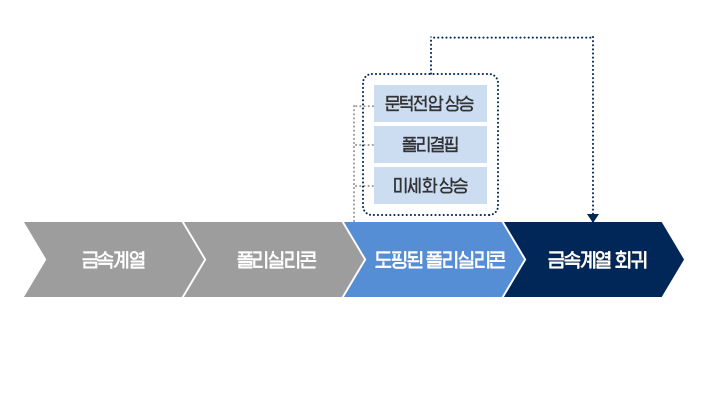

다시 금속성으로 회귀

▲ 게이트 물질의 변천 : 도핑된 폴리실리콘에서 금속계열로 회귀

TR의 크기가 점점 축소되면 게이트 옥사이드 두께 역시 동시에 작아집니다. 현재 게이트 옥사이드 두께는 약 1.2nm 정도까지 줄어들었고, 꾸준히 채널 길이와 함께 미세화 되면서 거의 1.0nm까지 줄어들고 있습니다. 그런데 구조가 축소되다 보면, 구조가 클 때에는 거의 영향이 없던 것들도 주변의 다른 도핑에 의해 영향을 쉽게 받을 수 있게 됩니다.

N_type으로 고농도 도핑된 폴리실리콘은 그 다음에 진행되는 P_type 관련 공정들로 인해 게이트의 N_type 공정의 도핑농도가 줄어들기도 하고, 게이트 옥사이드 두께가 얇아지면 게이트 층의 높은 농도가 옥사이드를 투과해 채널로 이동하기도 합니다. 게이트 농도가 줄어들면 (게이트 농도를 높여) 낮추려고 했던 문턱전압이 다시 약간 높아지게 되는데요. 이렇게 되면 결국 폴리결핍 현상을 줄이기 위해 폴리실리콘 계열을 사용했던 게이트 물질을 다시 금속 계열(텅스턴 등 용융점이 높은 물질)로 회귀하여 사용하기도 합니다. 단, 이때 게이트 옥사이드의 물질은 절연성이 좀 더 높은 High-K로 사용하여 2개 층을 묶어 HKMG(High K Metal Gate)라고 부릅니다.