반도체 칩을 동작시키려면 외부에서 여러 종류의 전압을 인가해야 합니다. 여기서 칩을 동작시킨다는 것은, 칩 내 수많은 트랜지스터(Tr)를 ON/OFF 시키거나 혹은 데이터를 셀에 저장하거나 지우도록 Tr 상태를 변화시키는 것입니다. Tr에 변화를 주려면 주로 4개의 전압이 개입해야 하는데, 이 전압들은 각각 Tr에 기여하는 정도가 다릅니다. 그리고 그 기여도에 따라 셀(Cell)이 집단 배치된 블록(Block) 속으로(혹은 기판으로) 수직축과 수평축 도선 통로를 따라 전압을 넣습니다. 이번 장에서는 메모리 소자들의 셀 배치와 그에 따라 각 셀에 입력되는 전압의 종류에 대해 간단히 살펴보겠습니다.

인가전압의 종류

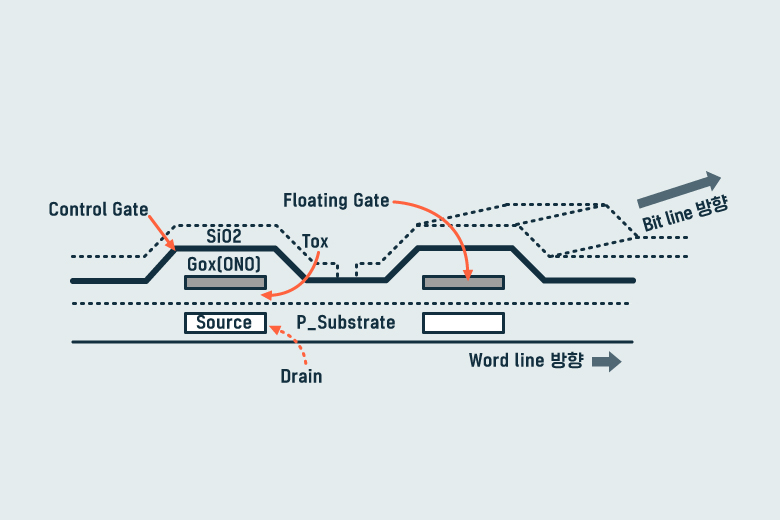

▲MOS Tr(Flash 디바이스)에 인가하는 전압의 종류(비휘발성 메모리인 경우) @ 출처: 'NAND Flash 메모리' 참조

nMOS 타입의 디램이나 플래시(NOR/NAND) 셀 1개만 놓고 보자면, 소스 단자에는 0V, 기판 밑에는 약한 (-)전압, 게이트 단자 및 드레인 단자에는 적당한 (+)전압이 인가됩니다. Tr을 동작시키는 관점에서 볼 때, 게이트 단자에 인가되는 (+)전압은 기판에 (-) 채널을 형성시키기 위한 목적이므로 가장 중요하다고 볼 수 있습니다. 드레인 (+)전압은 채널에 포진해 있는 전자들을 끌어들여야 하므로 두 번째로 중요하지요. 소스의 그라운드 전압은 각각 게이트와 소스, 그리고 소스와 기판 사이의 적정한 전위차를 유지하도록 사용하는데요. 디바이스 타입에 따라 별도로 인가하지 않는 경우도 있습니다. 마지막으로 기판에 인가하는 (-)전압은 p-type 기판에 항상 약하게 역방향 바이어스를 걸어 전자들이 기판을 통해 빠지지 않도록 하고, 동시에 기판 내부에 형성되는 여러 종류의 결핍 영역 두께 및 전자들의 흐름을 조절하는 역할을 하지요.

메모리 디바이스의 셀 구조와 전압 인가 방식

▲첫번째 이미지 : 메모리 디바이스의 셀 구조 / 두번째 이미지 : 메모리 디바이스의 셀 배치 @ 출처: 'NAND Flash 메모리' 참조

어느 디바이스든 각 셀을 동작시키기 위해 인가하는 전압은 크게 두 종류로 나뉩니다. 두 전압은 각각 게이트 단자와 드레인 단자에 인가되는데요. 게이트 단자로는 전압이 워드라인(Word Line, WL)을 통해 들어가고, 드레인 단자로는 비트라인(Bit Line, BL)을 타고 전달됩니다.

메모리 디바이스의 셀 구조는 병렬 방식과 직렬 방식이 있는데, 이는 비트라인에서 드레인 단자로 전압을 어떻게 인가하느냐에 따라 나뉩니다. 디램과 노어플래시의 셀 구조는 병렬 방식인 반면, 낸드플래시는 직렬 방식이지요.

메모리 셀의 동작 중에는 스위칭 작용이 가장 중요합니다. 그러므로 워드라인으로는 전압이 D램과 NAND는 무조건 모든 각 셀에 개별적으로 인가되는 병렬 방식이기 때문에, WL으로 직/병렬을 구분할 필요는 없습니다. 하지만, 비트라인에서는 Tr 기능과 집적도를 고려하여 인가전압 방식에 유리한 쪽으로 옵션을 걸 수 있습니다. 그중에 비트라인으로 들어가는 전압이 셀마다 직접 인가되는 형태가 병렬 방식입니다. 병렬 방식은 전압 인가 방식의 정석으로, 직렬 방식 역시 병렬 방식에서 파생된 것이라고 볼 수 있습니다.

병렬 방식 @ 노어플래시 전압인가

▲ 첫번째 이미지 : 노어플래시 디바이스의 셀 배치 @ 출처: 'NAND Flash 메모리' 참조 / 두번째 이미지 : 노어플래시 디바이스의 단면

노어플래시 셀은 워드라인과 비트라인 모두 병렬 방식입니다. 병렬 방식은 모든 셀의 드레인 단자에 비트라인을 거쳐 직접 전압이 인가되므로, 직렬 방식보다 소자의 동작속도가 빠릅니다. 하지만 비트라인이 각 셀까지 찾아가는 도로를 만들어야 하므로 연결되는 도로의 면적만큼 집적도는 떨어지지요. 따라서 비휘발성 메모리로는 셀 단가가 낮은 직렬 방식의 낸드플래시가 대세가 되었고, 노어 타입은 소자의 동작속도가 매우 빠르거나 신뢰성이 높은 특수한 경우에만 한정적으로 적용됩니다.

직렬 방식 @ 낸드플래시 전압인가

▲ 첫번째 이미지 : 낸드플래시 디바이스의 단면 / 두번째 이미지 : 낸드플래시 디바이스의 스트링 구조 @ 출처: 'NAND Flash 메모리' 참조

낸드플래시 셀은 워드라인은 병렬, 비트라인은 직렬 구조로 이뤄져 있습니다. 직렬 방식은 비트라인 방향으로 셀이 마늘을 엮어 놓은 듯 주렁주렁 매달려 있는데, 이를 스트링(String) 구조라고 합니다. 낸드플래시는 고유의 스트링 구조로 인해 노어플래시에 비해 집적도 측면에서 강점을 갖게 되었습니다. 그래서 현재는 비휘발성 디바이스의 97% 이상이 셀 당 최저 단가를 유지하고 있는 낸드플래시를 사용하고 있습니다. 다만, 낸드는 디램이나 노어에 비해 동작속도가 현저히 느리답니다.

낸드 셀에 비트라인을 통한 전압 인가 방식

▲ 낸드플래시 스트링 구조상의 전압 인가 방식 @ 출처: 'NAND Flash 메모리' 참조

한편 직렬 방식으로 인가되는 드레인 전압은 스트링에 달려 있는 수십 개의 셀 중 초입의 셀 1개만 인가됩니다. 따라서 스트링에 있는 모든 셀은 각각의 드레인 단자에 전압이 자동으로, 순차적으로 인가되도록 배치되었습니다.

즉, 스트링 구조에 따라 처음 1개의 셀에만 드레인 전압이 투입되면 나머지 수십 개의 셀에는 이웃의 소스와 드레인 단자를 공통으로 사용하면서 자동으로 드레인 전압이 인가되도록 하는 방식을 사용합니다. 물론 셀들이 직렬로 연결되어 있으므로 셀마다 발생하는 전압 강하는 감수해야 합니다. 셀의 전압 강하가 누적되어 전압이 한계치 이하로 떨어지면, 동작속도가 현저히 떨어지다가 소자의 동작 자체가 불능화됩니다.

전압 인가 방식이 집적도에 끼치는 영향

전압의 인가 방식에 따라 칩당 포함하는 Tr의 개수인 집적도에도 많은 영향을 끼칩니다. 디램의 현재(2019.01 기준) 주류 용량은 8Gb(DDR4)이고, 낸드는 128Gb TLC(하드웨어 용량 : 42.6Gb SLC)입니다. 하드웨어 용량을 기준으로 D램과 낸드를 비교해보면 최소 5배 차이가 나지요. (이는 디바이스를 어떤 용량을 기준으로 선택하느냐에 따라 달리 해석될 수 있습니다) 물론 디램은 커패시터가 점유하는 면적이 크지만, 병렬 구조에 따른 비트라인의 인입도선 및 병렬 특성으로 인해 셀이 추가적으로 어쩔 수 없이 점유하게 되는 영역도 많은 부분을 차지합니다. 반면 낸드는 디램에 비해 커패시터 점유 면적이 없으며, 직렬 구조의 셀 배치로 인해 절감되는 점유 영역 비율이 높다고 할 수 있습니다. 또한 직렬 방식의 셀 배치로 인한 집적도 증가는 낸드의 Technology가 항상 디램보다 앞서 나가는 데 기여하지요.

일반적으로 셀의 게이트와 드레인 단자에는 병렬 방식으로 전압이 인가됩니다. 하지만 낸드형 비휘발성 메모리는 모든 셀의 워드라인에 각각의 셀마다 병렬 방식으로 전압이 인가되는 반면, 비트라인에는 여러 개의 셀을 모아 초입 Tr 1개만 전압이 인가되는 직렬 방식이 적용됩니다. 이러한 방식은 집적도에서 장점을 갖지만 기능과 신뢰성에서는 뒤떨어집니다. 하지만 메모리 디바이스에서는 집적도의 장점이 다른 단점들을 대부분 압도하게 됩니다. 이번 장에서는 메모리 디바이스의 전압을 인가하는 직/병렬 방식(Block Level)을 알아보았는데요. 다음 장에서는 플래시 디바이스(비휘발성)의 게이트 단자에 전압이 인가될 때, 기판에 전달되는 과정에서 발생하는 전압강하에 대하여(Cell Level) 알아보겠습니다.

'정리하는 반도체 > 반도체 공학' 카테고리의 다른 글

| 반도체에서 자유전자 (0) | 2020.05.29 |

|---|---|

| 반도체 전자와 에너지 (0) | 2020.05.28 |

| DRAM과 NAND Flash 차이 (0) | 2020.05.25 |

| MOSFET의 Channel (0) | 2020.05.13 |

| Depletion 영역 (0) | 2020.05.12 |