반도체에서 가장 중요한 기능은 정확한 위치에 데이터를 저장하고 불러오며, 필요 없는 데이터는 깨끗이 삭제해 제때에 저장 공간을 확보하는 것입니다. 이렇게 반도체 제품이 가진 최소한의 성능을 일정 기간 동안 온전히 발휘할 확률을 ‘신뢰성’이라고 합니다. 기술이 발전함에 따라 반도체의 용량과 제품 종류는 다양해졌지만, 이러한 신뢰성은 계속해서 취약해졌다는 문제가 있습니다. 이번 장에서는 평면 타입(Planar type)의 비휘발성 메모리 2D NAND를 중심으로 보존성, 내구성, 교란성, 간섭성이라는 반도체의 네 가지 신뢰성을 알아보겠습니다. 그중 오늘 자세히 살펴볼 내용은 보존성(Retention)과 내구성(Endurance)입니다.

1. 반도체 고용량화에 따른 Cell의 결함 증가

<그림 1> Cell의 물리적 크기가 작아지고 Cell 간 간격이 좁아지는 경우 결함 증가

그동안 반도체의 설계 규칙은 Cell의 물리적인 크기와 간격을 끊임없이 줄이는 쪽으로 발전해 왔습니다. 이렇게 반도체 용량을 높이면 Cell당 가격을 매년 30% 정도씩 낮출 수 있지만 여러 가지 결함(Defect)이 생긴다는 문제점이 있습니다. 일단 Cell 자체의 크기가 작으면 외부 충격에 약해지고(보존성, 내구성), Cell과 Cell의 간격이 좁아지면 외부 전자로부터 받는 영향(교란성, 간섭성)이 증가하기 때문이지요. 따라서 이러한 고용량 반도체 Cell의 결함 증가율을 낮추기 위해 Cell의 위치를 바꾸거나(2D Planar→3D Vertical @낸드) 재질(High-K @절연층)을 바꾸기도 하고, 혹은 Cell 내 모양을 변경(FET→FinFET @Tr) 하는 등 다양한 기술적 변화가 시도되고 있습니다.

2. 반도체의 신뢰성 종류

NAND에서는 Cell의 회로 선폭(Pitch)이 좁아짐에 따라 크게 4개의 신뢰성 결함이 생깁니다. 먼저 내부적 결함으로 데이터 보존성(Data Retention) 약화와 데이터를 저장하고 지우는 능력인 내구성(Endurance: Program/Erasure Cycling) 문제가 있습니다. 외부적 결함으로는 Victim Cell이 자신과 이웃한 Cell에 저장된 전자 집단의 정전력에 영향을 받아 발생하는 데이터 에러, 즉 교란(Disturbance), 데이터를 저장하고 지우는 과정에서 Cell 주변에 임시로 갇힌 전자들이 영향을 주는 간섭(Interference)이 있지요.

<그림 2> 낸드의 핵심 신뢰성 항목

위의 네 가지 결함을 전자의 움직임이라는 관점에서 본다면, 보존성(Retention)과 교란성(Disturbance)은 움직이지 않는 ‘정전자’에 영향을 받는 현상이라고 할 수 있습니다. 반면 내구성(Endurance)과 간섭성(Interference)은 움직이는 전자들에 의해 영향을 받아 발생하는 신뢰성 결함이라고 할 수 있습니다.

3. 데이터 보존성(Retention)

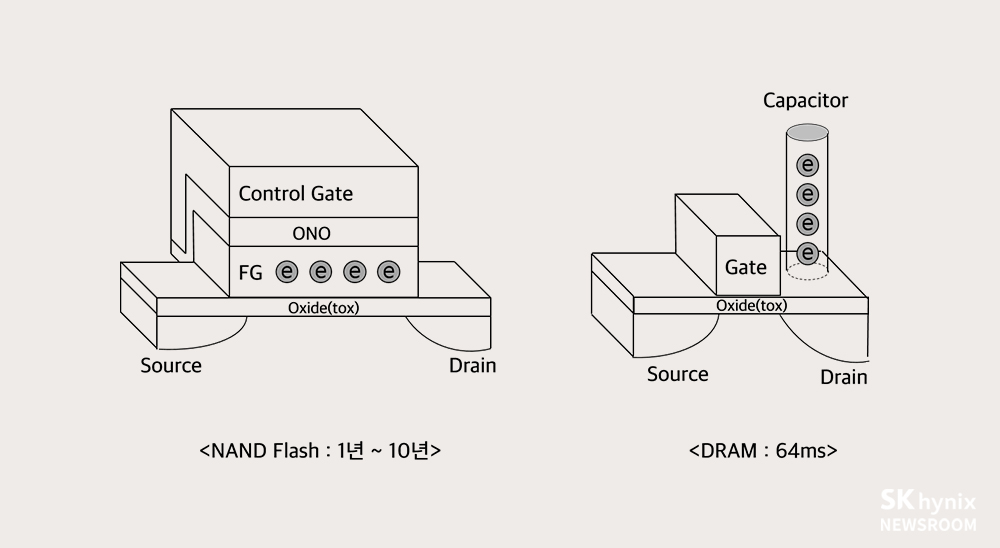

<그림 3> 데이터(전자 집단)의 저장 위치 @ 낸드와 D램

IT 기기에 보관된 모든 데이터도 언젠가는 사라지기 마련입니다. 비휘발성 FG NAND 메모리의 가장 핵심적인 신뢰성 요소는 보존성(Retention, ‘유지성’이라고도 함)을 꼽을 수 있습니다. 즉 플로팅게이트(Floating Gate)에 데이터를 얼마나 오랫동안 저장할 수 있느냐 하는 것이지요.

한편 휘발성 메모리인 D램의 경우 전원이 꺼지는 순간 데이터가 저절로 삭제되므로 오랜 시간 저장할 필요는 없습니다. 다만 전원이 꺼지기 전까지의 Refresh Time(64ms) 동안은 Tr를 거쳐 들어간 전자가 반드시 커패시터 안에 제대로 머물러야 데이터 손실을 막을 수 있습니다.

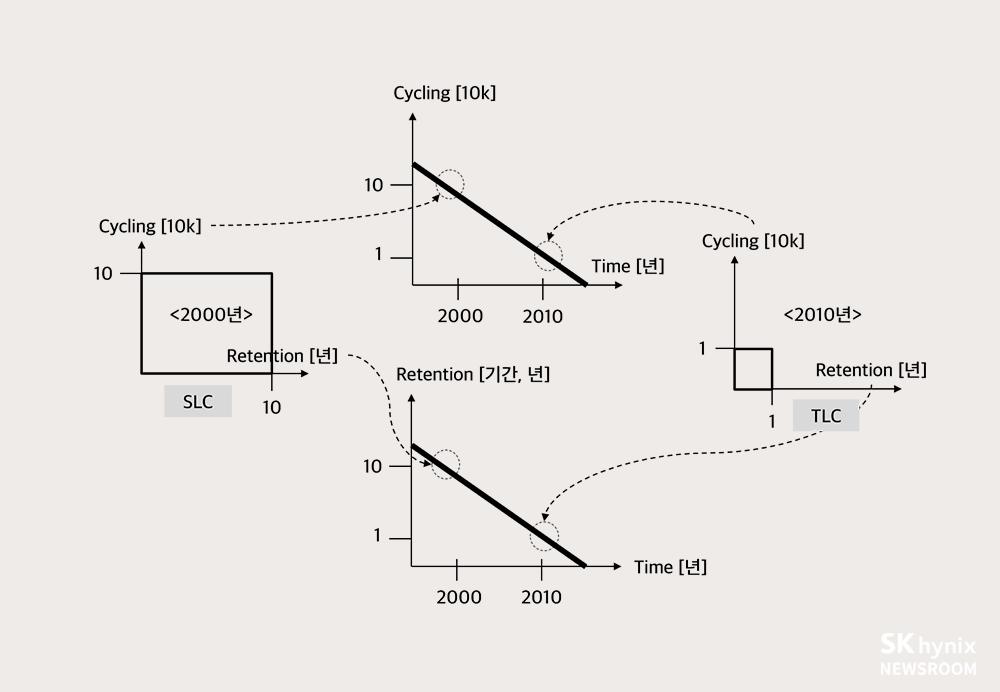

<그림 3-1> Technology 고도화에 따른 데이터 보존 기간 약화 @ NAND

신뢰성은 용량이나 속도 등 제품 기능이 향상될수록, 혹은 반도체 Cell의 면적이 줄어들수록 떨어지는 특성이 있습니다. 가령 비휘발성 메모리인 NAND는 제품에 따라 Cell 당 최대 1년(TLC) ~ 10년(SLC)까지 전자를 저장할 수 있어야 합니다. 하지만 Cell의 크기가 작아져 플로팅게이트의 입체 면적이 줄어들면 절연막이 얇아지고 전자의 터널링 작용으로 금이 가기 쉽고, 그 틈으로 전자 누수가 발생할 가능성이 커집니다. 그뿐만 아니라 한 번에 저장할 수 있는 전자 개체 수 역시 적어져 데이터 보존 기간도 짧아지게 되지요.

D램 역시 회로 선폭(Pitch)이 좁아지면 커패시터(Capacitor) 밑변도 함께 작아져 전자들을 저장(Charge)하기 어려워집니다. 특히 밑변의 길이가 20nm까지 좁아지면 종횡비(Aspect Ratio, 밑변 길이 대비 높이의 비율)가 100 이상이 되는데, 이는 커패시터의 형태가 비정상적으로 위로만 긴 ‘홀쭉이’ 상태임을 뜻합니다. 이렇게 되면 커패시터가 도미노처럼 옆으로 넘어질 확률이 높아집니다.

<그림 3-2> Technology 전개에 따른 D램 커패시터 형성에 대한 난이도 증가

이처럼 Cell의 크기는 줄이면서 커패시터의 종횡비(AR) 값을 높이지 않기 위해서는 반도체 공정 과정 역시 복잡해질 수밖에 없습니다. 따라서 노광 공정이 제일 중요했던 과거와 달리, 최근에는 식각과 세정 공정, 증착 공정 등 다른 공정에서 요구되는 기술이 더욱더 까다로워지고 있습니다. 커패시터나 절연층의 재질을 High-K 물질로 바꾸거나, Cell의 모양과 배치까지 바꾸는 식이지요.

4. 내구성(Endurance)

우리가 핸드폰이나 컴퓨터로 사진이나 문서 작업을 통해 데이터를 저장하고 지우기를 반복하는 과정은 그 자체로 Cell에 스트레스를 주는 것과 같습니다. 이렇게 저장과 소거를 반복하는 동작을 Cell이 최대 몇 회까지 견딜 수 있는가를 측정하는 것이 내구성(Endurance)입니다.

<그림 4> 데이터를 저장(Program )하고 소거(Erasure) 하는 PE Cycling 동작 @낸드

데이터를 ‘저장’(Program=NAND) 하고 ‘소거’(Erasure) 하는 동작을 한 번 반복하면 1회 Cycling이라고 표현합니다. 따라서 내구성은 ‘PE Cycling(Program/Erasure Cycling)’이라고도 부릅니다. PE Cycling 1k는 Cell 당 최대 1,000회까지 데이터를 저장하고 지울 수 있는 것을 의미합니다. 신뢰성이 높은 반도체가 되려면 보존성뿐만 아니라 내구성도 함께 높아야 합니다.

5. 보존성과 내구성의 비교

결국 보존성(Retention)과 내구성(Endurance)은 NAND 동작상의 신뢰성(Operational Reliability)을 의미합니다. 보존성은 플로팅게이트에 전자들을 가두어 빠져나가지 못하도록 하는 능력이고, 내구성은 반복적인 PE Cycling 수행에 대한 한계 조절 능력이라고 할 수 있지요. 이 둘 사이는 상충관계 혹은 교환 가능한 거래 관계(Trade off)이기 때문에 한쪽을 강화하면 다른 한쪽이 약화합니다. 가령 CTF-type은 내구성을 강화하면 보존성이 약해지고, FG-type은 보존성이 강한 대신 내구성이 약합니다. 특히 FG-type은 PE Cycling을 하면 할수록 Cell 내부의 분자 간 인력이 낮아지므로 궁극적으로는 절연막에 금이 생겨 보존성도 떨어지게 됩니다.

<그림5> 보존성과 내구성의 제품별 및 시기별 비교

NAND는 FG 기반의 SLC(Single Level Cell) 출현 이후 5년 단위로 MLC(Multi Level Cell)를 거쳐, TLC(Triple bit MLC)까지 진화했습니다. 그러나 신뢰성의 차원에서 볼 때 TLC는 10년 전에 출시된 SLC보다 10분의 1에 불과한 신뢰성 능력을 갖추고 있습니다. 다양한 설계 도식과 알고리즘의 개발에도 불구하고 FG와 FG 사이의 간격이 좁아지면서, 보존성과 내구성을 일정 수준(Cell 당 3년-10k Cycle 수준)으로 유지하기에는 역부족이었습니다. 즉 NAND 제품이 SLC>MLC>TLC로 진화하면서 Cell 당 용량은 높아졌지만, 신뢰성 측면에서는 2D-Planar type에서 오히려 점점 더 불리해지는 상황이 되었다고 할 수 있겠습니다.

반도체 제품의 기능(속도, 정확도 등)과 신뢰성 사이에서도 상충관계가 있고, 신뢰성 내의 항목들끼리도 서로 거래 가능한 관계(Trade off)가 있어서, 제품 스펙을 정할 때 전반적인 능력을 조율하여 적정한 수준의 제품 레벨을 설정합니다. NAND 제품이 SLC > MLC > TLC로 진화함에 따라 전반적인 신뢰성이 약화하였고, 특히 최근 양산되고 있는 QLC의 경우 PE-Cycling이 거의 불가능하고 데이터 읽기 기능만 가능한 수준으로 신뢰성이 가장 낮습니다. 한편 3D의 등장으로 FG-2D-MLC에서 CTF-3D-TLC로 바뀌면서 보존성은 약화하고 내구성은 강화되는 부침이 있었고, 이를 보완하고자 개별 Cell의 구조, 재질 등에도 변화가 생겼습니다. 또한 칩 내에서도 Cell의 성격이 상이한 Area(Storage Area 혹은 Coding Area)별로 신뢰성 항목을 각기 다르게 설정하여 맞춤형으로 Fab 공정을 진행하기도 합니다.

'정리하는 반도체 > 기사 정리' 카테고리의 다른 글

| 반도체 업계, 코로나 19 악재 속에서도 '차세대 기술 개발' 박차 (0) | 2020.05.05 |

|---|---|

| 메모리 반도체의 신뢰성(2) - 교란성과 간섭성 (0) | 2020.05.03 |

| 시스템 반도체 육성 위해 정부와 기업이 뭉쳤다 (0) | 2020.05.02 |

| 블록체인 (0) | 2020.05.01 |

| 삼성전자, 반도체 EUV 공정 두가지 난제 (0) | 2020.04.30 |